Best Books for Mastering VLSI Design Verification

VLSI • Verification • Reading List

Even seasoned verification engineers benefit from authoritative, field-tested books. This curated list highlights

community-favorite titles—with SystemVerilog, UVM, and formal/ABV—balancing academic rigor and

practical, tapeout-driven methodology.

SystemVerilog and Constrained-Random Verification

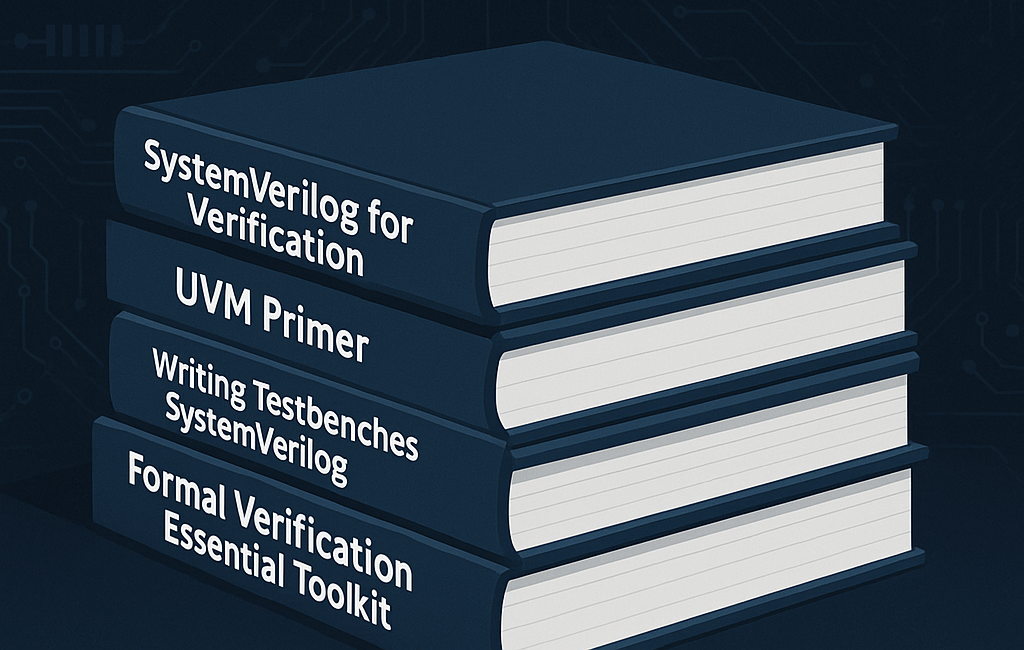

SystemVerilog for Verification (3rd ed.) — Chris Spear & Greg Tumbush

Coverage: classes • randomization • assertions • functional coverage • UVM intros

Why it stands out: A comprehensive, example-rich path from basics to advanced testbench design;

doubles as a desk reference for day-to-day SV verification.

- Strength: One-stop textbook with exercises and proven best practices.

Writing Testbenches Using SystemVerilog — Janick Bergeron

Coverage: architecture • stimulus • checking • coverage • results analysis

Why it stands out: Methodology-first blueprint aimed at first-time success; language-agnostic insights implemented with SV.

- Strength: Clear, scalable verification planning and architecture guidance.

UVM (Universal Verification Methodology) Guides

The UVM Primer: A Step-by-Step Introduction to UVM — Ray Salemi

Coverage: OOP in SV • drivers/monitors/agents • env/top assembly

Why it stands out: Accessible and example-driven; gets engineers productive with UVM quickly.

- Strength: Beginner-friendly yet complete path to hands-on UVM.

Advanced UVM (2nd ed.) — Brian Hunter

Coverage: patterns • coding guidelines • chained sequencers • scaling strategies

Why it stands out: Distills expert patterns beyond the user guide for robust, high-throughput environments.

- Strength: Practical “recipes” that improve reuse, performance, and maintainability.

Formal and Assertion-Based Verification

Formal Verification: An Essential Toolkit for Modern VLSI Design — Erik Seligman, Tom Schubert, M.V. Achutha K. Kumar

Coverage: property checking • assertion writing • formal coverage • equivalence

Why it stands out: Pragmatic, staged methodology to adopt formal alongside simulation.

- Strength: Stepwise integration of formal into existing flows with real examples.

SystemVerilog Assertions & Functional Coverage (3rd ed.) — Ashok B. Mehta

Coverage: SVA language • assertion strategy • functional coverage • labs

Why it stands out: Comprehensive SVA + coverage guide for both dynamic and formal flows.

- Strength: Practical scenarios for complex checkers and coverage models.

Finding Your Way Through Formal Verification — Bernard Murphy, Manish Pandey, et al.

Coverage: when/where to apply formal • technique overview • planning

Why it stands out: Concise primer by Synopsys experts; lowers the barrier to getting value from formal.

- Strength: Manager- and engineer-friendly introduction without heavy math.

Verification Methodology & Planning Fundamentals

Principles of Functional Verification — Andreas Meyer

Coverage: goals • planning • metrics • directed vs. CRV • co-simulation • case studies

Why it stands out: Timeless, language-agnostic strategy to align architectural intent with implementation.

- Strength: Big-picture guidance on plans, coverage, resources, and project risk.

Conclusion

These titles are the gold standard for modern verification—spanning SystemVerilog, UVM, and formal/ABV.

Whether you’re scaling a regression farm or writing your first assertion library, investing in these books

pays back in fewer escapes, cleaner sign-off, and faster tapeouts.

FAQs