While AI and digital compute dominate headlines, the quiet surge in analog is reshaping teams, schedules, and hiring. This article walks through the markets, circuits, and layout skills driving unprecedented demand—and what it means for students and early-career VLSI engineers.

The Market Inflection: IoT, Edge, and Automotive

The numbers are unambiguous: the data-converter market is projected to climb from roughly $5.6B (2024) to $8.7B (2033), while automotive PMIC revenue is on track to double from about $4.1B (2024) to $8.6B (2033). Three megatrends explain the pull:

- IoT sensor proliferation → Precision analog front-ends (AFEs) and efficient, quiet power rails.

- Edge computing → Tight latency and power budgets push analog fidelity to the forefront for ML at the edge.

- Automotive/ADAS → Radar, LiDAR, cameras, and ultrasonics require robust, low-noise AFEs and safety-ready multi-rail power.

Data Converters: Where Precision Meets Throughput

ADCs and DACs translate real-world physics into bits. State-of-the-art high-speed ADCs now reach ~128 GS/s with around 5.5-bit ENOB, illustrating the classic speed/precision trade-off across Flash, SAR, and Sigma-Delta architectures.

[Image: ENOB vs. Sample Rate by Architecture]

Caption: Flash excels at speed, ΣΔ at resolution, SAR hits the IoT/automotive sweet spot.

The new demand is for smarter converters—on-chip calibration, adaptive filtering, and integrated power management. Noise specs matter strategically: noise spectral density in the −140 to −165 dBFS/Hz range often decides a system’s SNR budget.

Power-Management ICs: The Unsung Hero

Behind every reliable measurement sits a quiet, stable rail. The broader PMIC market is trending from ≈$39.4B (2024) to ≈$64.8B (2032). Modern PMICs orchestrate multiple domains with soft-start, sequencing, telemetry, and fail-safe behaviors.

LDOs illustrate the leap: sub-200 mV dropout, ultra-low IQ (down to ≈0.3 µA), and high PSRR are now table stakes for sensor nodes and safety-critical rails.

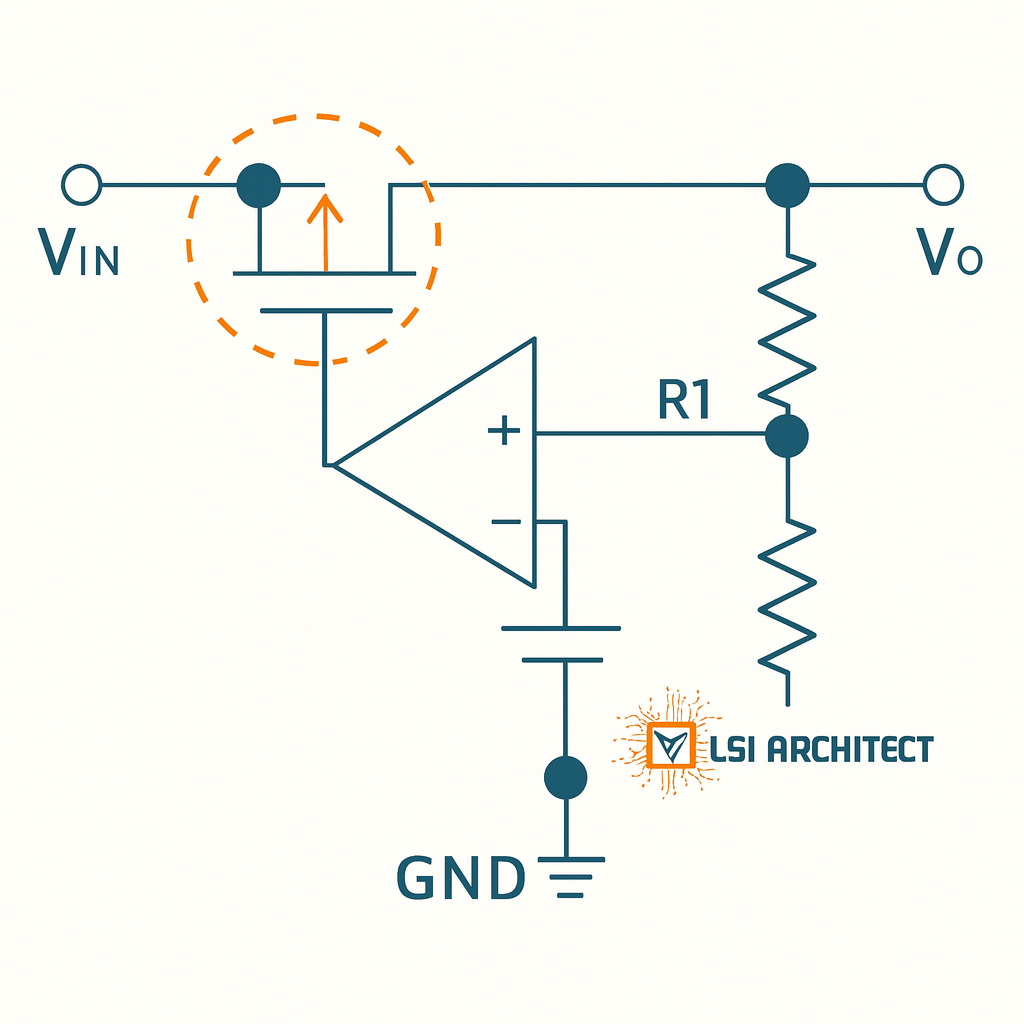

[Image: LDO Dropout Curves Across Load Current]

Caption: Why P-channel LDOs still matter—better low-dropout behavior extends battery life in edge nodes.

Analog Layout Mastery: Art That Moves the Needle

Matching & symmetry

Common-centroid and interdigitation are essential in mirrors and differential pairs. The four layout rules—coincidence, symmetry, dispersion, compactness—directly suppress random and systematic errors.

Guard rings & isolation

From substrate contacts to deep-N-well strategies, good ring design reduces latch-up risk and substrate noise coupling. In advanced nodes (e.g., 16 nm FinFET), guard-ring-aware placement has demonstrated area reductions approaching ~50% without degrading performance.

Dummy devices & uniformity

Dummy gates/devices stabilize etch/loading and improve OPC accuracy. In recent studies, ML-assisted dummy placement delivered ≈8.4× speedups while maintaining analog QoR.

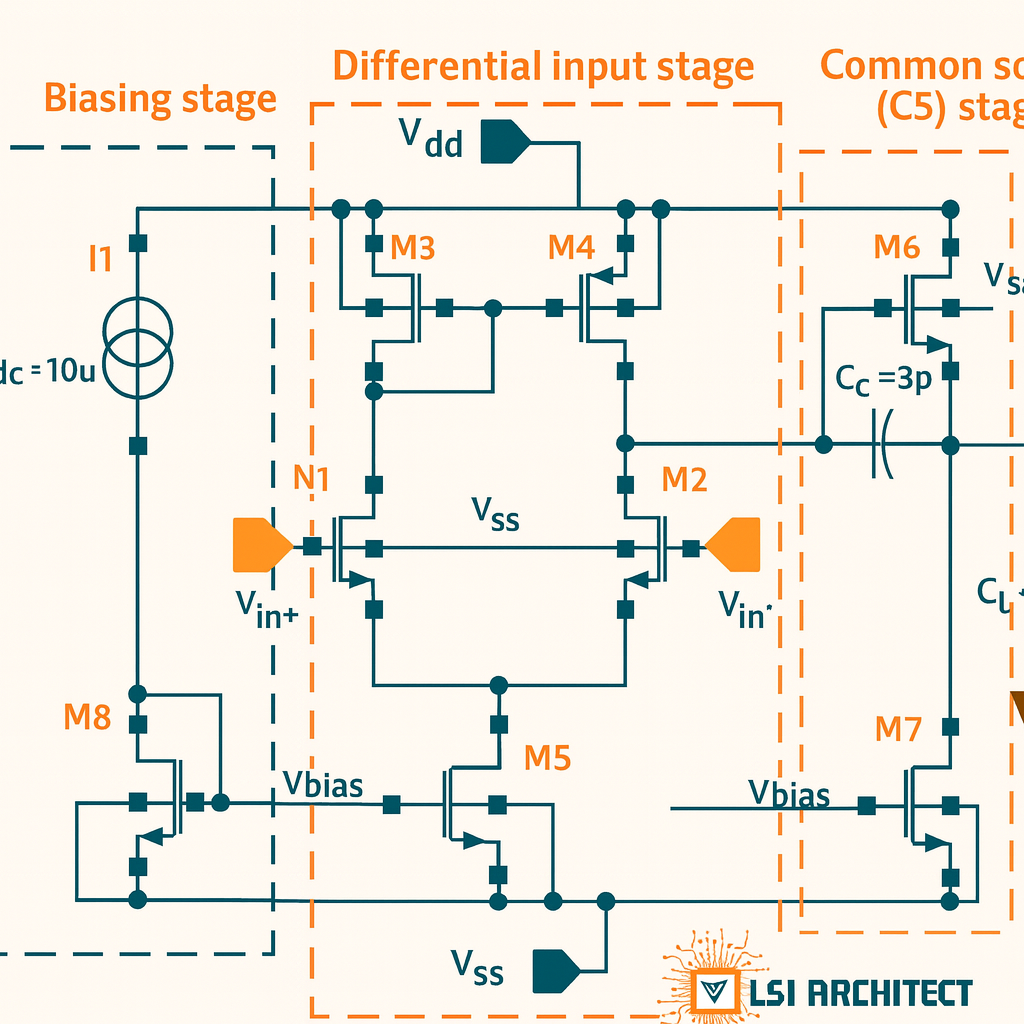

Modern Op-Amp and LDO Topologies

Precision & fully differential op-amps

For precision AFEs and high-resolution ADC drivers, designers target CMRR > 130 dB and low 1/f noise. Chopper-stabilized amplifiers deliver near-zero offset with careful charge-injection control and PVT-robust stability.

Next-gen LDOs

Cap-less designs and fast-transient LDOs achieve microsecond-class settling for dynamic loads. First-order efficiency is η ≈ V_out / V_in—every millivolt of dropout translates to measurable energy savings in long-life IoT nodes.

Lab Exercise: PEX Impact on a Differential Pair

Pre-layout sims rarely tell the whole story. Post-layout extraction (PEX) exposes routing capacitance, well proximity effects, and substrate coupling that can add >10 mV of offset in naïve layouts.

What to measure:

- ΔV_OS from asymmetrical parasitics

- CMRR degradation from imbalanced metal paths

- GBW/phase shifts due to added C_par

- Noise rise from substrate coupling

Hands-on idea: Lay out a matched pair with and without dummies, guard rings, and common-centroid placement; compare PEX vs. schematic.

The Economics of Analog Expertise

Job data and community threads align with what hiring managers see: analog remains scarce and complex. Senior/principal analog roles often demand a decade of mixed-signal experience—compensation is trending upward as SoCs absorb more sensing, power, and reliability content.

Outlook: The Analog Renaissance

Expect continued pull from 5G/6G, autonomous systems, edge AI, and renewables. The winners bridge the analog-digital divide—turning real-world physics into robust bits while managing power, noise, and reliability.

In an increasingly digital world, the engineers who understand electrons—not just bits—will write the next chapter.

Call to Action

Ready to go deeper with hands-on training? Build precision AFEs, stabilize LDOs, and validate layouts with PEX. Explore our Analog IC Design and Analog Layout Design programs to start your portfolio.

FAQs