“MAGICAL: An Open-Source Fully Automated Analog IC Layout System from Netlist to GDSII”: A Review

In the evolving landscape of semiconductor design, automation has redefined digital IC workflows—yet analog IC layout has long resisted full automation. This gap is precisely what MAGICAL (Machine Generated Analog IC Layout) aims to bridge. Developed by Hao Chen et al., MAGICAL is an open-source, fully automated analog IC layout synthesis framework capable of generating tape-out–ready GDSII layouts directly from unannotated netlists and design rules.

For VLSI engineers, CAD tool developers, and researchers seeking next-generation analog automation, MAGICAL represents a significant leap forward—combining constraint-driven design, machine learning, and end-to-end workflow integration.

1. Why MAGICAL Matters in Analog VLSI Design

While digital design flows benefit from complete RTL-to-GDSII automation, analog layout remains manual, iterative, and highly expertise-driven. This makes analog IP development costly and time-intensive.

MAGICAL changes this by offering:

Open-source accessibility for academia and startups.

Benchmark circuits for reproducibility.

Integration capability with existing open-source EDA stacks.

Source: MAGICAL – Official Site

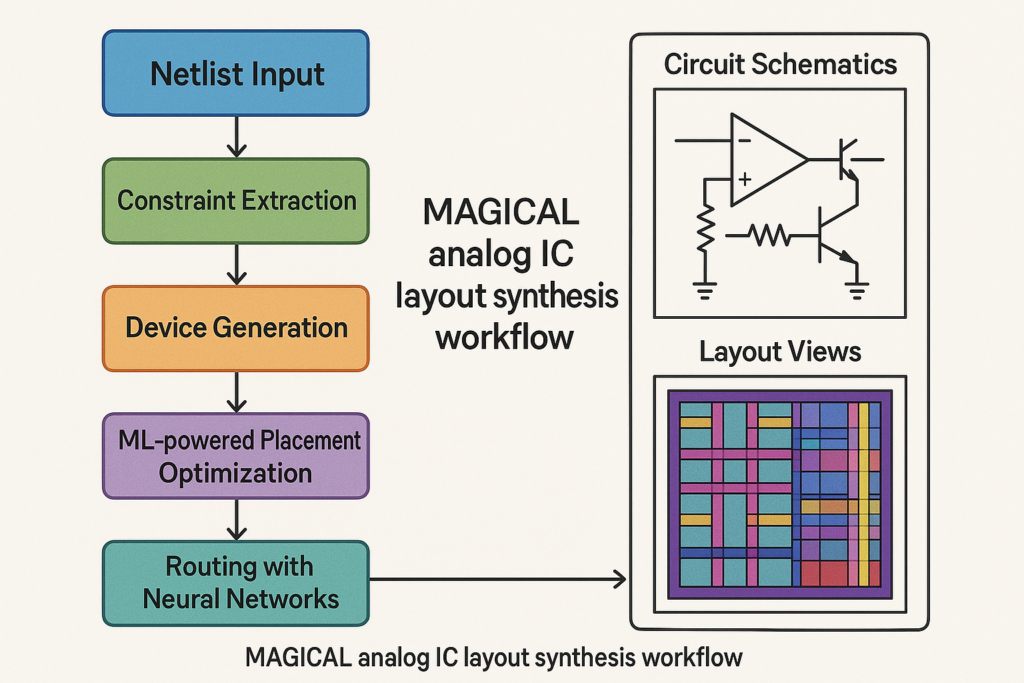

2. End-to-End Automation: From Netlist to GDSII

MAGICAL’s pipeline addresses every key step in analog layout design:

Constraint Extraction – Detecting symmetry, matching, and critical routing requirements.

Device Generation – Auto-generating transistor fingers, capacitors, and resistors per DRC rules.

Placement Optimization – Multi-objective optimization balancing wirelength, area, and symmetry.

Constraint-Aware Routing – Using ML models for symmetry-compliant interconnects.

Post-Layout Verification – Validating DRC, LVS, and PEX with industry-standard tools.

3. Machine Learning Integration in MAGICAL

Unlike rule-only based systems, MAGICAL incorporates AI at multiple stages:

WellGAN – GAN-based well structure generation.

GeniusRoute – VAE-powered routing path optimization.

ML-Driven Placement Scoring – Predicting quality before committing to placement.

Bayesian Optimization – Iterative tuning of layout performance.

4. Technical Breakdown for Advanced Readers

4.1 Constraint Extraction

Graph-based symmetry detection.

Mapping device-level and system-level constraints.

Ensuring matched components are placed and routed in compliance.

4.2 Device Layout Generation

Automated parameterized cell (PCell) creation.

Native DRC-correct geometries for MOSFETs, resistors, capacitors.

Extensibility for custom device generators.

4.3 Placement Engine

Analytical placement with LP legalization.

Multi-objective optimization (wirelength, symmetry, performance).

Pre-placement evaluation using neural networks.

4.4 Routing System

Symmetry-aware global and detailed routing.

Grid-based A* search with constraint cost functions.

ML-assisted routing for analog-critical nets.

4.5 Validation Flow

DRC/LVS/PEX via Calibre.

Direct import to Cadence Virtuoso for post-layout analysis.

5. Experimental Results

Two-Stage OTA

Gain: 69.7 dB (MAGICAL) vs. 69.8 dB (manual).

UGB: 1496 MHz vs. 1567 MHz.

Offset: 0.027 mV vs. 0.012 mV.

CTDSM

Nearly identical power.

Slight SNDR/SFDR degradation compared to handcrafted layout.

Observation: Comparable performance to manual layouts with a dramatically reduced design cycle.

6. Current Limitations

Parasitic Modeling – Lacks comprehensive coupling/IR drop awareness.

Commercial Tool Integration – No native Cadence/Synopsys/Mentor links.

Advanced Node Support – Validated at 40nm; unproven at sub-10nm FinFET.

Performance Tuning Overhead – Bayesian optimization still requires multiple iterations.

7. Future Development Roadmap

Enhanced AI-driven parasitic-aware performance optimization.

OpenROAD integration for mixed-signal co-design.

FinFET-ready device generation.

Expanded analog/mixed-signal benchmark libraries.

8. Strengths vs Limitations – At a Glance

| Strengths | Limitations |

|---|---|

| Open-source, democratizes analog automation | Limited advanced-node validation |

| Fully automated, netlist-to-GDSII | Needs tighter commercial EDA integration |

| ML-enhanced placement & routing | Parasitic-aware optimization not fully implemented |

| Performance comparable to manual layouts | Bayesian tuning iterations still needed |

9. Why This is a Game-Changer

For the VLSI Architect training audience, MAGICAL is not just a research curiosity—it’s a practical bridge between academia and silicon.

It offers:

Real-world automation examples for teaching.

A sandbox for CAD research without NDA restrictions.

A rapid prototyping platform for analog IP in startups.